# CompLex (VC-SPG)

An OpenSoundControl (OSC) and Voltage Controlled Signal Path Generator

Lex van den Broek

Master Thesis

Instrument & Interfaces

Institute of Sonology - Steim

Royal Conservatoire, The Hague (NL)

May 2017

Supervisor: Edwin van der Heide

#### Abstract

This thesis describes my electronic and artistic research into the design of what I have called the Voltage Controlled Signal Path Generator (VC-SPG). It is a switching audio matrix that can both be seen as a new tool, and as a part of a musical-instrument. As we will see, it can be applied in an analogue electronic music studio setup, a modular synthesizer or in an interactive art-installation. This master research project is a continuation of my previous work at the Royal Conservatoire where I design new technology for Art and Education.

The fundamental core of my research project is the development of an audio-matrix with 16 inputs and 16 outputs that can be fully configured, controlled and programmed with Open Sound Control (OSC) and that can be synced and triggered with external analogue signals. In its present state the VC-SPG has become a new type of generator that is able to switch between different studio presets and form the core of new audio experiences and new compositional approaches.

I will describe and reflect upon both the technical challenges and development and the musical and artistic results shared with me by students and professionals who used the VC-SPG over the last year for their own work. They all experienced the VC-SPG to be adding a new dimension to their creative process. We can conclude that the VC-SPG is not only a new practical tool, but also a creative instrument for electronic-music and art.

# Acknowledgements

A project like this can't be developed successfully without the help and input of dedicated coaches, colleagues, students, family and friends. Thank you all for helping me. I want to thank some people who really spend time and effort to give my thoughts new direction.

Lots of thanks to my wife Anita - she is a great support. Edwin, thanks for being my supervisor, for coaching and support and for pushing my thoughts into new directions - I needed that! Johan and Robert, I liked our fruitful brainstorm sessions. Let's continue these sessions! My coaches at Steim, Kristina and Joel. Thank you for the inspiring chats.

Since I'm always in my office at the Conservatoire developing, programming, measuring, testing, teaching and coaching, a lot of people drop by on weekly bases for a coffee, a favor or a chat. Many of these chats were of great help for my research as well. Sometimes it's about the things that are not being said, that triggers my thoughts and ideas. My colleagues at the EWP, thanks for your support and giving me time to do this project.

Kees, Marko, Paul, Siamak, Richard, Frank, Jo, Kasper, Justin, Raviv, Peter, Ruben, Guiliano, Andrea, Kyriakos, Chris, Rolf, Diana, Karst, Kacper and Max: Thanks!

# Content

| Acknowledgements                                                       |                                          |

|------------------------------------------------------------------------|------------------------------------------|

| Abstract                                                               |                                          |

| 1. Introduction                                                        |                                          |

| Analogue studio general configuration                                  | 1                                        |

| Signal paths                                                           | 2                                        |

| Pre-research activities                                                | 4                                        |

| From idea to research                                                  | 5                                        |

| Stockhausen studio matrix                                              | 5                                        |

| RC studio project                                                      | 6                                        |

| Search for equivalent devices                                          | 88                                       |

| 2. The VC-SPG basics                                                   | 9                                        |

| 3. Hardware design                                                     | 1                                        |

| The microcontroller                                                    | 12                                       |

| AD75019 chip                                                           | 13                                       |

| The Lantronics Xport                                                   | 14                                       |

| Operational Amplifiers_                                                | 18                                       |

| CV and Trigger adjustment                                              | 16                                       |

| Circuit layout                                                         | <br>17                                   |

| Printed Circuit Board                                                  | 18                                       |

| SPG prototypes                                                         | 19                                       |

| 4. Software design                                                     |                                          |

| Assembly                                                               | 22                                       |

| Data transfer example                                                  |                                          |

| SPG main-routine                                                       |                                          |

| External and internal interrupts_                                      |                                          |

| Receive OSC interrupt                                                  |                                          |

| Timer interrupt                                                        |                                          |

| Signal change interrupt                                                |                                          |

| Sequence routine                                                       |                                          |

| Max/Msp                                                                |                                          |

| 5. VC-SPG Features                                                     | 3/                                       |

| Initial startup                                                        | 3£                                       |

| Mixing function                                                        | 3£                                       |

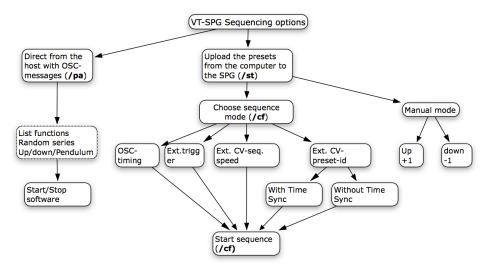

| Sequence with the SPG                                                  |                                          |

| OSC as a source                                                        |                                          |

| External triggers                                                      |                                          |

| CV-speed                                                               | 30                                       |

| CV-preset_                                                             | 40                                       |

| Audible clicks                                                         |                                          |

| SPG switching quality                                                  | 41                                       |

| 6. SPG Communication                                                   | 4:                                       |

| OpenSoundControl (OSC)                                                 | 47                                       |

| OSC messages                                                           | 10<br>4!                                 |

| patch (pa)                                                             | 10<br>4!                                 |

| store (st)                                                             | 46                                       |

| configuration (cf)                                                     | 10<br>47                                 |

| SPG and network communication                                          |                                          |

| SPI serial protocol                                                    | ''<br>48                                 |

| RS-232 serial protocol                                                 | <sup>⊐C</sup>                            |

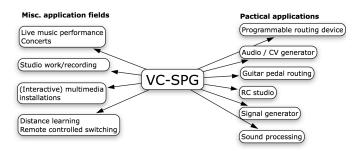

| 7. Applications and roles                                              | □                                        |

| VC-SPC Roles                                                           | د⊏ ـ ـ ـ ـ ـ ـ ـ ـ ـ ـ ـ ـ ـ ـ ـ ـ ـ ـ ـ |

| VC-SPG Roles                                                           | د۳<br>۲۱                                 |

| Programmable routing device Signal routing and automation (for guitar) | 51<br>51                                 |

| Live performance tool                                                  | د ع                                      |

| Remote studio                                                          | <sup>52</sup>                            |

# Content (continued)

| Audio and CV generator                    | 53 |

|-------------------------------------------|----|

| Remote signal routing                     |    |

| 8. Musical and artistic results           |    |

| My personal results                       |    |

| Artistic results                          |    |

| Software results                          |    |

| 9. Conclusion                             |    |

| Future technical ideas and recommendation | 64 |

| Appendices_                               | 66 |

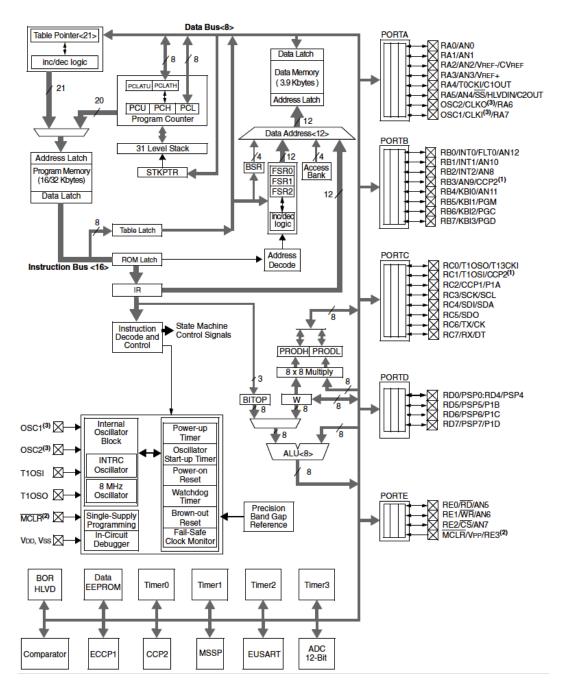

| A Block diagram PIC18f2523                | 67 |

| B PIC18F2523 _pinout                      | 68 |

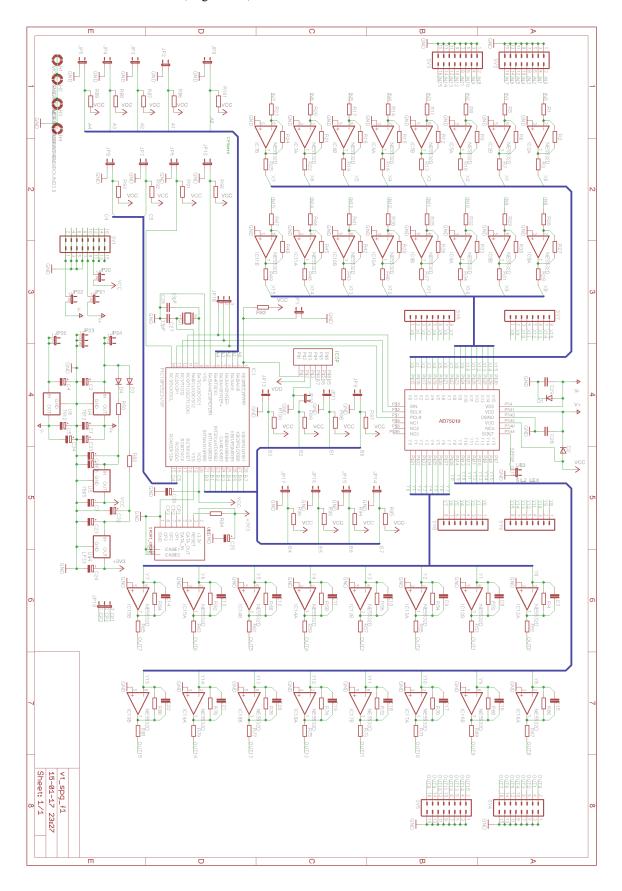

| C Circuit-layout                          |    |

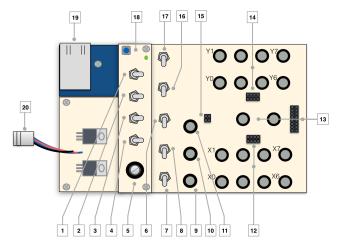

| D1 Model 1                                | 70 |

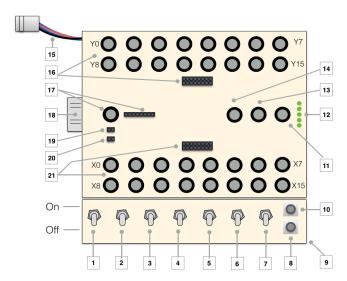

| D2 Model 2                                |    |

| D3 Model 3                                | 74 |

| D4 Model 4                                | 76 |

| D5 Model 5                                | 77 |

| D6 Model 6                                | 78 |

| E Flowchart Interrupt                     | 79 |

| G Max/Msp patch                           | 80 |

| H Printed Circuit Board (PCB)             |    |

| I Assembly code (v95)                     | 82 |

| J VC-SPG specifications                   |    |

| Bibliography                              |    |

| Endnotes                                  |    |

#### 1 Introduction

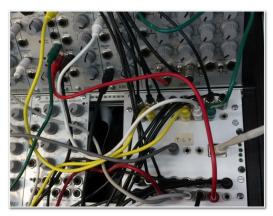

Working in an analogue electronic music studio environment requires working with patch cables enabling the studio user to interconnect all types of sound modules in order to generate sounds. Modular synthesizer setups also depend on making inter-connections first, before all the aspects of the sounds can be explored. To this day the connections or patches in electronic studios or modular-synths are created with wires connecting inputs and outputs. These connections are still static.

In this master-research project I will introduce and explore the electronic design of a new type of instrument, that is capable of changing these hardwired connections, and can dynamically switch between presets controlled by a remote computer or by external signals.

What would the influence be in the way electronic music is composed when this signal path generator will be part of an electronic-studio? Will the introduction of this generator give the composer a new tool to compose electronic music and if so, how will it be applied? To be able to answer these questions, I have built multiple models of the VC-SPG (Voltage Controlled Signal Path Generator) to give users the opportunity to test, evaluate and explore its potential.

### 1.1 Analogue studio configuration

As head of the Electronics Workshop (EWP) at the Royal Conservatoire, I experience a lot of studio-configurations in general, but especially electronic studios. Electronic studios, much like modular synths, consist of a lot of different sound devices, effect processors and individual modules and in combination with sound-recorders, computers, audio-mixers and loudspeakers new sounds and new music can be explored and created.

The design of the analogue studio of Sonology, which is a classic voltage controlled studio and is based upon the use of an analogue patch panel. See figure 1.1. Working in this studio means you have to make the right interconnections between different modules and make setting and adjustments to create effects like modulation, pitch change, timbres, volume-change and many more effects and sounds.

Figure 1.1. Analogue studio Bea-5 with the patch-panel (on the right) where all ins and outs are located.

In the first year of the master research project, Kees Tazelaar<sup>1</sup> introduced me to the

fundamental control-voltage techniques and explained to me the analogue-studio philosophy. Since the original project title was to design a patch-generator, the difference between the word 'patch' and hardwired connections are a source for discussion. According to Kees, and I agree with him on this point, a patch is not only a hardwired connection between two points, but it is a combination of the connection with the right settings of the linked modules. If the frequency range of a generator and the wave-shape selection is changed, also the resulting sound will change and that change of sound is independent of the hardwired connection. In other words, not only the connection or routing of the wires make the sound, it's the combination of the settings and the connections together that define the word 'patch'.

The patch-cables provide hard connections between inputs and outputs of the different sound- and effect-modules (e.a. triggers or control-voltages). The output of one module can drive the input of other module(s). The patch itself, consisting of multiple cables and the right settings, determines which inputs and outputs are inter-connected and defines the range of sounds that are created in the studio-setup. Currently the position of the patch-cables can only be changed manually. The patch itself is static and will only change if the user changes the connections manually.

My research involves the design and realization of an interface that can switch in total 256 connections or 16 inputs and 16 outputs simultaneously. It can switch the connections triggered by an external signal, so the studio or modular synth itself can be used to control (and sync) the moment of switching to the new preset or patch. Furthermore there are two control voltage inputs that determine the speed of the sequence and that determine the 'id' of the next preset in line ( the sequence order).

Since the beginning of this research I also noticed that a matrix of 16 in and 16 out is not really enough to cover all connections in a regular studio setup, but it is a beginning and it will be enough to investigate whether this interface is an interesting new composition-tool.

# 1.2 Signal Paths

Back in the days the computer was not yet a part of our daily live, telephone connections were manually fixed by people sitting in front of huge panels. From the first moment analogue synthesizers were (commercially) used in the beginning of the 60's, the sounds produced were dependent of the physical connections created with cables. The combination of the different modules that were connected with these cables formed the core of the synthesized sound and this was, and now still is, a very static connection with patch-cables.

Figure 1.2

Once the connections were made and the fundament of the sound generation was found, the limits could be explored only within the boundaries of these hard-wired connections. With big studio setups it could require an effort to re-patch every connection and the patches made had to be well documented. Already back then the time available in an expensive analogue studio was limited and the users wanted to use their time in the most effective way possible. An ingenious system was invented to store and re-call hard wired connections, in order to save precious time. See figure 1.3. The wires were connected to a transportable or portable plate, that could be removed and re-installed so the physical connections were stored and re-called.

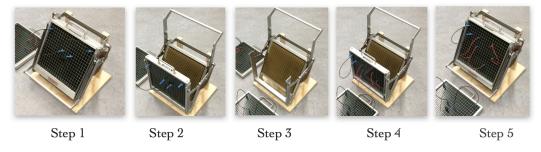

Step 1 shows the (very simple) active patch. The storage-device showed in figure 1.3, was integrated in a studio setup attached to the back of the device. In step 2 the lever is moved upwards to detach the plate from the actual patch-panel. Step 3,4 and 5 show how the new patch is moved in place and 'activated' by moving down the lever.

To create connections between two or more points, you need wires. These wires make a physical connection between the output of one device and the input of another. At least that is what was required in the old days and it still holds true today.

Figure 1.3. Switching between presets, old style.

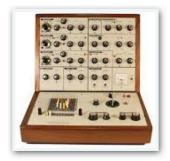

At the end of the 1960's the EMS company created the VCS3 (Voltage Controlled Studio version 3). The physical cables were replaced by pins and with placing one pin between two points in the matrix (one row and one column) a connection between modules was made. The use of the matrix within these VCS3 synths formed a part of the

inspiration to develop a fully automated matrix version, introducing the possibility to work with dynamic and time-based connections as part of the sound generation and composition of electronic music.

Figure 1.4. The VCS3 Synthy or Putney

#### 1.3 Pre-research activities

In 1996 I started working for the Electronics workshop (EWP) at the Royal

Conservatoire in The Hague. My electronics mentor and colleague Jo Scherpenisse<sup>2</sup> and I started with the design of one of the first small sensor-interfaces in that time, the Microlab. The Microlab was a small MIDI<sup>3</sup> sensor-interface with 5 analogue inputs and a 7-bit resolution. It could be assembled and built by students themselves and it was cheap enough for them to also purchase. The design was based upon an (for that time), advanced Microchip PIC16F series microcontroller. Being able to convert changing voltages into 7-bit MIDI controller data, was a great step forward for the creation of musical interfaces and interactive installations. Students were now able to build their own MIDI-instrument and control digital processes with signals that originated from the physical world by using sensors.

The next step in the development of new interfaces was the inverse. The possibility to convert digital MIDI data into physical control and actions. For example conversions into CV (Control Voltage), servomotor drive, relay switching, stepper-motor drive, pulse width modulation (PWM) and many more. With this new technology, the students could realize more innovating musical instruments and interactive installations. A lot of the instruments and installations built at that time were based upon this technology — see some examples in figure 1.5.

Figure 1.5 Ipson64, IpsonCompact and OSC-CV board

After working with MIDI for several years and teaching students how to apply this technology and after my colleague Jo Scherpenisse retired, I continued with the design of new electronics and the search of new ways for faster communication and higher control resolution. MIDI in that time was and still is limited to a 10-bit (0-1024 steps) resolution and had a relative slow bitrate of 31,25 kbit/s. In my search for new technology, starting around 2004, I encountered Open Sound Control (OSC)<sup>4</sup> as a new musical communication protocol. I also discovered a small embedded web server component, called the XPort. This Xport is a complete embedded web server that communicates using ethernet connections or Wifi. The combination of the Xport and OSC opened up a new world for me to design new OSC-sensor interfaces, like for example the IpsonLab and the IpsonCompact©.

#### 1.4 From idea to realization and research

The idea for developing an audio-matrix that can be fully controlled through OpenSoundControl and that can be driven by analogue voltages and external triggers actually arose because of multiple practical requests within the Conservatoire: the introduction of a new mixing console in the Karlheinz Stockhausen-studio<sup>5</sup> and the introduction of new V-FUG's in analogue studio Bea-5 and the refurbished VCS-3 synthesizers with its classic patch-panel matrix. All these subjects, combined with my OSC interface design experience, contributed to the idea of this research project.

### 1.5 Stockhausen studio matrix design

The initial request that motivated me to look into new types of switching circuits, was the purchase of a new mixing console for the Stockhausen studio at the Royal Conservatoire. The old mixer that had to be replaced because of its age and constant growing technical problems, was originally designed and built by technicians of the Institute of Sonology. This audio-mixer was equipped with some very impressive routing capabilities that were not to be found in any other modern mixing console.

It had the possibility of routing a lot of different sources directly to the main faders and from there to the four big JBL loudspeakers. For composers working frequently in the studio it was of great importance that this feature would be restored if a new mixer was to be installed. One of the practical reasons was the position of the audio-mixer, the recorders and the four loudspeakers in the studio. Sometimes it was necessary to listen to the left-

and right-speaker working behind the audio-mixer and in other moments, when controlling the recorders and being turned 90 degrees, two other speakers had to be the left- and right one. With the push of a button the routing of the signals to the speakers could be changed.

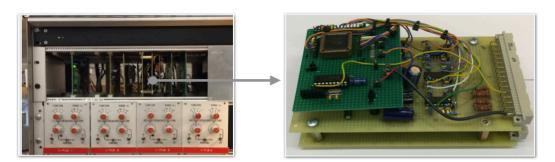

The request to re-design this feature in the KHS-studio was the reason for me to look into a solid and more modern switching solution for the first time. I designed a first version of the matrix and re-introduced this unique routing possibility back into the KHS-studio with the use of a small chip called the AD75019 audio switching array (see figure 1.6).

Figure 1.6. Design sheet, electronics and final result of the routing matrix for the KHS-studio.

In the new setup the old matrix-switches still were used to drive the new designed matrix-electronics. Every separate push-button selected a different signal-path from the source, directly to the speakers.

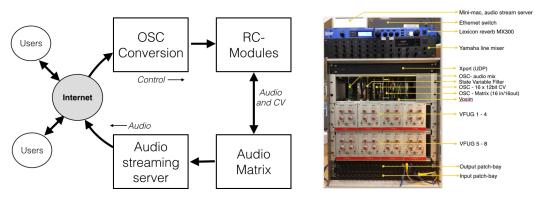

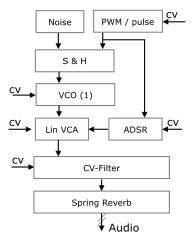

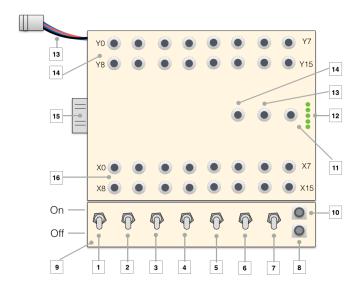

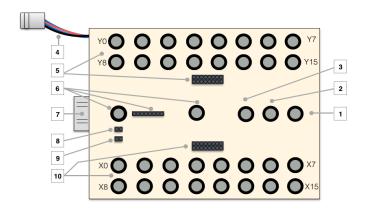

The remote-controlled studio, or RC-studio, forms a side track of my research and actually represents the start of the VC-SPG research. This modular synthesizer-setup consists of different modules in one 19-inch rack which are all inter-connected through the first version of the matrix interface — see figure 1.7.

Figure 1.7. The first matrix-board for the RC-studio

The RC-studio is a small analogue modular synthesis system, with 8 x VFUG (Voltage controlled Function Generator), one VOSIM (Voice Simulation), one VSF (Variable State Filter), a matrix and multiple VCA's (Voltage Controlled Amplifiers) that all can be remotely controlled with OSC. The generated audio result is streamed to the internet and

can be listened to by anyone connected to the internet — live, self-played, internet radio.

Figure 1.8. RC-studio block diagram (left) and the actual device (right)

The idea to design a RC-studio was realized in small steps and started in 2009 after or during building the matrix for the Stockhausen studio. It started with the installation of 12 brand new VFUG's in analogue studio Bea-5, leaving the 8 old VFUG's unused and waiting to be refurbished, modified and re-used. In that time, I also designed a new 12-bit OSC-CV board and the VFUG's, which have a voltage input to control the frequency, presented themselves to be a great testing object to listen to the pitch-change driven by OSC. This test-setup was the first step in the creation of the RC-studio and it offered me the ideal platform to test new digital to analog conversions.

Of course a remote controlled pitch-change for the VFUG driven by OSC-messages is not enough to fully control the VFUG and the features had to be extended. The next step was controlling the switches located on the front of the modules for selecting the wave shape and frequency range of the VFUG. The switches on the front are therefore bypassed with physical relays and are also controlled by OSC-messages - yet another conversion: OSC to relay control. And since it also is important for any analogue studio to be able to make inter-connections between different modules, the router design already created for the Karlheinz Stockhausen studio, could be used as a remote controlled patch panel. This was the next step in the creation of the RC-studio, the integration of a remote controlled patch-panel, designed with the AD75019 audio matrix switch array Controlled by digital data, this audio matrix can be used to change analogue signals and connections. See figure 1.7.

The AD75019 is a chip that can make hard connections between multiple points. A hard connection means the change of resistance between infinity (no connections and therefor equals the off position) and 150 ohms (equals the on position). The switches are also bi-directional, which indicates the current can flow both ways.

For the implementation of the AD75019 in the design of the matrix, I added operational amplifier (opamp) circuits to the input and the output. The main reason for this choice was

the addition of the creation of the audio- and control voltage summing feature. When multiple inputs are selected to be routed to one output, all these inputs will be added (mixed) correctly by the opamp summation circuit (inverting amplifier).

#### 1.6 Search for equivalent devices

During the development of the first model of the VC-SPG, I searched the internet for a device with the same features that I had in mind for the VC-SPG: 16 x audio inputs, 16 x audio outputs, programmable and controllable with the computer and able to work standalone, controlled by analogue signals.

The first Google searches for 'OSC matrix' is pointing to my own website (www.ipson.nl), where I describe an older version of a matrix board that can be driven with OSC. After some more extensive search I found a version of an equivalent matrix board, named the Sequential Switch Matrix<sup>6</sup>, see figure 1.9. This Eurorack module has 4 inputs and 4 outputs and is manually programmable and does not support OSC. It does have control voltage inputs and the Eurorack module is specially designed to be part of a modular synth only.

Figure 1.9 The sequential switch matrix.

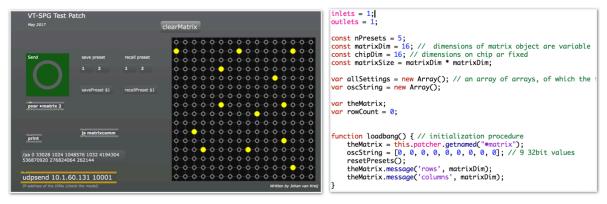

#### 2 The VC-SPG basics

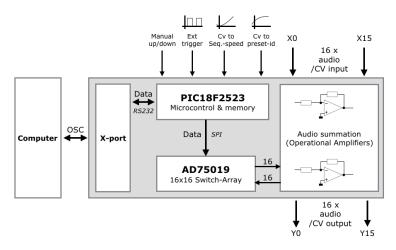

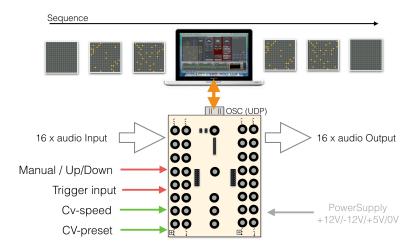

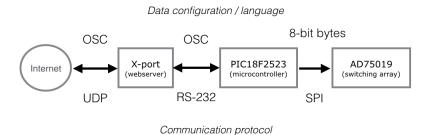

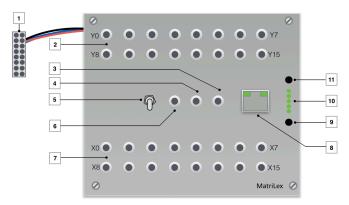

The projects described in the introduction, in combination with my expertise of controlling analogue and digital electronic signals, were the key ingredients for the design of the first version of the VC-SPG. The following section covers the main features of the VC-SPG including its routing architecture. Figure 2.1 shows the block-diagram of the complete VC-SPG, designed around the PIC18F2523 microcontroller running the self developed assembly firmware, the AD75019 switching-array and the embedded webserver, called the X-port.

Figure 2.1. The gray block shows the complete interior of the SPG interface.

The fundamental feature of the VC-SPG is the possibility to dynamically control analogue signal-paths (patch cables) with the use of a computer and by means of external voltage-triggers and/or control-voltages. In combination with the self-developed Max/Msp patch (see page 32) the created signal-path presets can be activated sequentially, played-back from a list or the presets can be uploaded to the local memory of the SPG. In total 32 connections can be changed with one trigger or click. The SPG has a local memory that can store up to 32 different presets, all with their own preset-id. If the presets are stored in local memory, it can operate stand-alone and sequence through these presets by itself without the computer connected, making it a real hybrid between the digital- and analogue world. A sequence of steps through the presets, at high or low speeds, can be controlled and synced by external control voltages or triggers. This turns the SPG into a generator, generating sequences of changing physical connections.

The VC-SPG, or CompLex as a few students already nicknamed it, is a programmable and voltage triggered audio-matrix. The SPG has 16 inputs and 16 outputs, all able to handle signals in the audio range between -12V and +12V. The communication is performed with OpenSoundControl (see page 43) over an ethernet connection and the interface has 3 external analog control inputs (see figure 2.2):

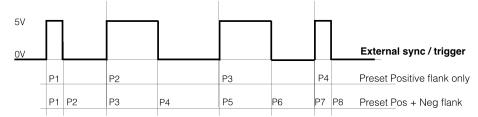

- 1. The external trigger input can be connected to an (audio) pulse changing between 0V and 12V, and whenever this signal changes its value from 0V to 12V (rising edge) or from 12V to 0V (falling edge), the VC-SPG will step to the next preset in local memory. With this input the VC-SPG can be synced with external processes and change presets accordingly.

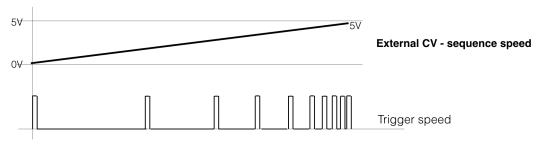

- 2. The control voltage to speed (CV-speed) input converts incoming voltage changes to the speed of the sequence. If the CV input is low (0V), the VC-SPG will step through the local stored presets with a low speed. High sequence speeds are achieved with higher values of the CV input.

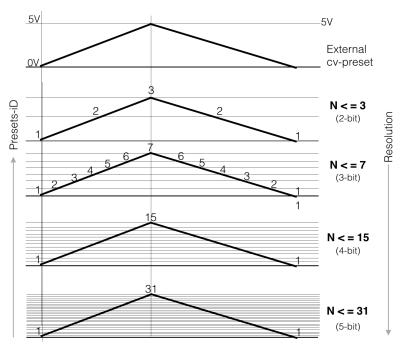

- 3. The third input converts the voltage value to a preset-id. Changing the voltage on this input, will also activate the corresponding preset.

The VC-SPG can be used in many different scenarios, but there are two mainstream applications. First the use in combination with a computer connected running software generating OSC-messages and the second application without the computer connected, stand alone. In figure 2.2 a computer is connected and either way it will always initiate with a computer connected due to the fact that an initial set of presets has to be programmed and stored in the VC-SPG.

Figure 2.2. Block diagram of the VC-SPG communicating with the Max/Msp patch

The next two chapters 3, Hardware and 4, Software both describe the pure technical design approach of my research project. Since I designed a complete new instrument that consists of hardware and software, it is of importance to share these detailed technical aspects and topics in this thesis. For those readers, who actually do not have any technical background, it may be more suitable to advance to chapter 5, "VC-SPG Features" on page 35.

### 3 SPG Hardware design

To create a device like the Voltage Controlled Signal Path Generator (VC-SPG), a combination of main components is needed, which will be focussed on in this Hardware section.

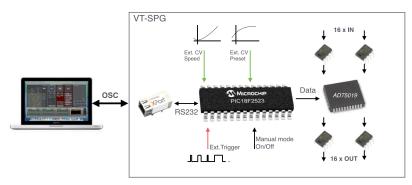

Figure 3.1

First of all the embedded web server, or Xport, as main communication port. This webserver, made by Lantronics, sends and receives UDP and TCP-IP data to and from the network and converts this data into the RS-232 serial data protocol<sup>7</sup> ( see communications chapter for more detailed information). The brain of the design is the PIC18F2523 microcontroller which handles all incoming- and outgoing-data, reads the analogue signals and drives the switching process. The actual switching is realized with the Analog Devices AD75019 switching audio matrix.

In this chapter I will focus on the important properties of these main components and explain them. The hardware design of the whole device is somehow generic when you compare it with most of the OSC-devices I already designed: the Xport transmits and receives the OSC-messages and communicates this data-flow with the microcontroller (see figure 3.1). The self-developed assembly software within the microcontroller (also called firmware) determines the functionality and will decide what actions will be taken. The complete data flow and Assembly design will be covered in chapter Software design starting on page 22.

As shown in figure 3.1, the X-port sends and receives OSC-messages and communicates directly with the microcontroller using the RS-232 protocol. Depending on the received OSC-message address-tag and data content, the microcontroller will send the appropriate switch information to the matrix and the audio matrix configuration will be changed accordingly. To be able to drive the SPG with analogue external signals, the microcontroller can also receive control-voltages or trigger-pulses and convert these signals to switching information. An important part of the functionality of the SPG is also determined by the specially developed Max/Msp software patch that can be used to control and program the SPG from a computer.

#### 3.1 The microcontroller (PIC18F2523)

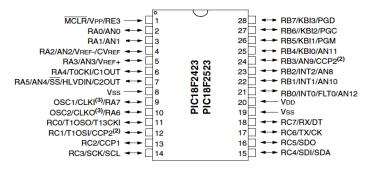

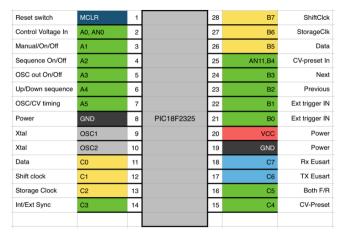

"A 28-pin enhanced flash microcontroller with 12bit A/D and nanoWatt technology"8. That's the main title of the Microchip data-sheet or user-manual, containing 390 pages full of detailed information. Because the PIC18F2523 is the main component of the interface design, it is of big importance to explain some of the main features of this controller. The PIC18F2523 package is a 28-pin DIP (dual in line) chip that has 28 physical pins to be connected. Like most chips, or active components, this controller needs two pins for the power connection +5V (VCC) and 0V (GND).

Pin 1 of the controller, see figure 2, is the master-clear pin. When this pin is connected to 0V (GND), the program running inside the microcontroller, also referred to as the firmware, will reset the program running inside and it will restart from the top.

Figure 3.2. The pin-out of the PIC18F2523 and the package.

Check appendix A for a complete block diagram of the PIC18F2523 microcontroller. Like any microcontroller, almost all the pins are inputs and/or outputs, clustered in ports. This particular 28 pin controller has three of those 8-bit ports, called porta, portb and portc. The pin names referring to these ports start with a capital R, followed by A, B or C (see figure 2). All ports are 8-bit wide which means portb for example consists of portb,0 (=RB0) until portb,7 (=RB7), making 8 bits in total. All communication with the peripherals (the X-port, the audio matrix, the switches) is realized through these 3 main ports. Within the text and the figures in this document, the port-numbers are also referred to as RB0 (= portb,0) or RA5 (=porta,5).

As part of the multifunctional design of the microcontroller, multiple functions are gathered in one pin. Depending on the configuration of the microcontroller or initialization part of the process, the pins will have a specific function. This all starts with the definition of inputs and outputs within. All three 8-bit ports can be inputs and/or outputs within the same application. The definition of inputs and outputs within the design of the interface is a puzzle and often the choice of the type of microcontroller depends on how many inputs and outputs it has.

See figure 3.3). The colours are used to divide the signals into different categories.

Green is input for the controller, these can be control-voltages or switches. Yellow is data communication using the SPI protocol (Serial Peripheral Interface), where pin 11, 12 and 13 transfer the data to the audio switching array and pin 26, 27 and 28 are communicating the preset numbers in manual mode to the 5 external led's. The light-blue colour indicated the connection with the X-port, communicating RS-232 with the processor (Rx = receiving and Tx = transmitting). The black and red colours are used for the power supply and one dark blue connection is used to indicate the master clear (MCLR) pin. In appendix B this same figure with more detailed information about all individual pins can be consulted.

Figure 3.3. The pinout of the microcontroller with SPG functionality.

#### 3.2 AD75019 16 x 16 Crosspoint Switch Array

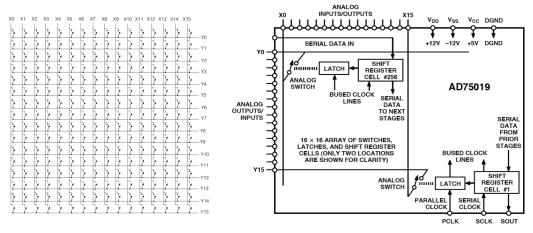

The main component of the VC-SPG that does the physical switching is the AD75019, made by Analog Devices. This chip contains 256 analogue switches in a 16 x 16 array (see figure 3.4. The switches are bi-directional, which means either the X or the Y can be input or output. Because the design of the chip is based on CMOS<sup>9</sup>, the resistance of the switches in 'on' position is 150 Ohms and in 'off' position the value is infinite. The datasheet of the chip describes this: "the AD75019 is fabricated in Analog Devices' BiMOS II process. This epitaxial BiCMOS process features CMOS devices for low distortion switches and bipolar devices for ESD protection". In the design of the VC-SPG the direction of the signal is determined by the additional operational amplifiers (opamps) which function like an audio buffer and audio mixer and it defines the input and output.

Figure 3.4. 256 switches in a matrix and the functional block diagram of the AD75019.

Besides the power connections of -12V, +12V, +5V and GND the AD75019 has three connections for the data communication: the PCLK, SCLK and SIN. The method of transferring the switch information from the processor to the array is also referred to as SPI or I2C. In the chapter 'SPG communication' (page 43) this method is explained in more detail. SIN is the serial data input and all data passes through this input. The (switch) data is 'clocked in' with the SCLK. This is a pulse signal changing from 0V to 5V at a high frequency rate. Every time this signal changes from 0V to 5V, also called the rising edge, one bit is clocked into the onboard data register. Per writing cycle for the whole array, this has to be done exactly 256 times. After all bits have been 'clocked in' into the data-register, the new status of the switches has to be activated. This is done by changing the PCLK signal, which on a falling-edge (5V to 0V), will store and activate the new switch configuration.

#### 3.3 The Xport

The Lantronics X-port is an embedded ethernet device server and is designed to add serial capability to any electronic device that has serial communication available. The Xport can receive and send UDP/TCP-IP packages from the internet and convert this to the serial communication protocol RS-232. The component looks like a single RJ45 connector (figure 3.5), but on the inside a complete 32-bit processor is running to process all incoming and outgoing data.

Figure 3.5. The X-port, a complete embedded ethernet device server.

The Xport has a RS-232 input and output which within the configuration of the SPG both are directly connected to the Tx and Rx ports of the microcontroller. The OSC-messages that are send from the computer to the SPG use UDP (User Datagram Protocol) to travel over the net. UDP is a standard data protocol. When the OSC-message is received by the X-port, the data is converted to RS-232 and transmitted to the microcontroller.

To configure the X-port and tweak its settings a standard web browser is used. During the building process of the SPG, the Xport is already configured and tweaked to be the perfect communication partner for the microcontroller. The only variable that has to be set if a new user is connected to the SPG, is the remote IP-address (this is the IP-address of the user).

### 3.4 Operational Amplifiers (Opamps).

When audio signals are being patched, mixed or switched it is almost always realized with the use of operational amplifiers, or opamps. An operational amplifier is an ideal building block for all kind of electronic applications, but especially for handling audiosignals.

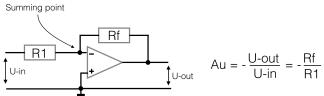

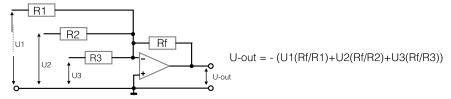

An opamp has 3 important properties, that make it ideal for electronics. (1) It has a very high input impedance which causes the current flowing into the opamp to be almost zero. (2) The amount of amplification between in- and output is possibly infinite. Without feedback compensation the output of the opamp will always hit the positive- or negative power-supply rails. (3) It has a very low output impedance, which allows the opamp to have a strong output current. The chapter 'Features' (see page 35) already focussed and describes the use of the opamps for the input and the output of the matrix. The circuits used for both input and output are called 'inverting amplifiers' and are one of the most common applied mixing circuit designs.

Figure 3.6. Inverting amplifier circuit.

Figure 3.6 shows an inverting amplifier with Rf (feedback) and R1. The ratio of these resistors determine the amount of amplification, and in case of the in-and output of the SPG, both resistors are 10kOhm - the amplification is -1. If in case of the SPG multiple inputs are selected to be routed to one output, a summing amplifier will be created, like shown in figure 3.7.

Figure 3.7. Inverting amplifier with multiple inputs and U-out is the sum of all inputs.

As already highlighted in chapter 'Features', connecting multiple inputs to one output is creating a perfect addition (mix) of the input signals on the output. If one input-signal is selected to be routed to multiple outputs, the inputs signal has to be split. With the configuration the SPG has currently, the amplitude of the input-signal will decrease every time the signal is split. Every time an input signal is split, multiple negative inputs of different opamps are tied together, confusing the amplifier circuit setup. There are solutions to this problem, but at this point this 'feature' is still not fully implemented.

#### 3.5 CV- and Trigger-input adjustment

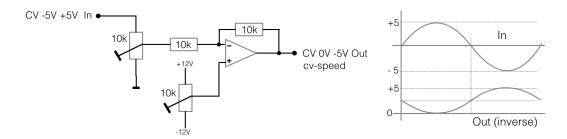

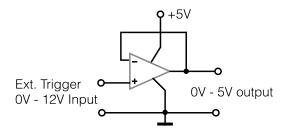

The SPG contains three external inputs that have to be conditioned before the signal can be fed to the input of the microcontroller. The microcontroller is so called TTL-compatible. This means the inputs of the controller cannot exceed voltages higher than +5V. A standard euro-rack modular system uses audio signals that vary between -5V and +5V. The pulses and triggers of this system are in between 0V and +12V (measured with the Doepfer A-100 system).

These values are too high for the microcontroller to process, and therefore these signals have to be conditioned. The variation from -5V to +5V has to be converted into 0V - +5V and the pulses have to be lowered from +12V down to +5V.

Figure 3.8. Conversion of the cv-speed is inverted.

The conversion from -5V to +5V is realized with an opamp circuit as shown in figure 3.8. The input control voltage (from the euro-rack system) is first divided by two with the use of a 10k potentiometer connected to the input. Because the input signal is connected to the negative input of the opamp(-), the output will be inverted (inverting-amplifier). Unlike the conversion of the control-voltage for the preset-id, this control-voltage has to

be converted due to the use of the onboard timer where a small number (= a low value) results in high frequency. The trimmer potentiometer on the positive input creates an offset voltage, so the new 'zero-crossing' on the output is lifted to 2,5V as shown in the graph. A similar circuit is used for the conversion of the CV-preset-id, except this conversion does not have to be inverted.

The external trigger pulse coming from the euro-rack modular is switching between 0V and +12V. This has to be converted in to 0V and +5V. There are multiple ways to realize this conversion, for example with the simple use of an avalanche-diode. An avalanche-diode has a certain threshold voltage after which it starts to experience an 'avalanche breakdown'. In other words, if the voltage parallel to the +5V-avalanche diode exceeds +5V, the voltage will not be higher than 5V because of the avalanche effect. The diode acts as a compressor.

In the modular version of the SPG the solution of an opamp was used. If an opamp has an applied power of +5V, the output will never exceed this 5V, because that's the maximum it can deliver. If +12V is applied to the input, the output will be +5V. Take a look at figure 3.9.

Figure 3.9. Follower circuit with opamp powered with +5V.

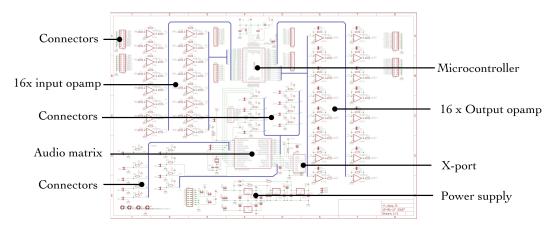

## 3.6 SPG circuit layout

Below in figure 3.10 the complete circuit layout is shown. A more detailed and extracted version of the same picture can be found in appendix C. In the process of designing a new device, drawing the circuit layout is not only very important for document reasons, but it is also the fundament for drawing the Printed Circuit board.

Figure 3.10 Full schematic of the VC-SPG (minus the additional modifications)

Drawn with Eagle software, the circuit-layout shows all the main components, some smaller components and the power-supply all inter-connected to the right pins. There is a difference between the thin red wires and the thicker blue wires used in the circuit-layout. The thicker blue wires are so called 'busses'. They consist of multiple wires going to and coming from the same component. Busses are normally used to route address-lines or datalines. Using these multi-wire busses in a layout creates a clearer view of the circuit instead of drawing every wire separately, like the red-ones. The biggest surface of the circuit is used for the 32 operational amplifiers, 16 times input and 16 times output (see page 35).

The one part that is not drawn in this circuit layout, but will be added an updated version, is the adjustment of the control voltage from -5V/+5V into 0V/5V and the adjustment of pulses from 0V/12V to 0V/5V. This part of the circuit is added in a later stage and will be part of a modification for the next model.

A very important and obvious part is the power-supply section. The SPG uses three intern voltage regulators to create +12V, -12V, 5V and 3,3V. The use of +12V and -12V (balanced power-supply) is a common way of powering operational amplifiers and audio electronics in general. Audio-signals, or AC- signals, move from positive- to negative values and if these signals have to be modified (amplified, filtered, muted, etc ...) a broad dynamic workspace is needed to realize this. Hence the balanced power-supply.

The +5V, a part of the external power adapter as well, is used for the digital electronics inside the SPG. It powers the microcontroller and the digital part of the audio-matrix. The 3,3V, extracted from the +5V with a LF33 voltage regulator, feeds the current consuming Xport. The Xport needs quite some current to operate, around 200mA in quiescent state.

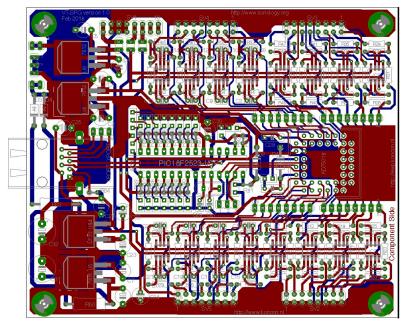

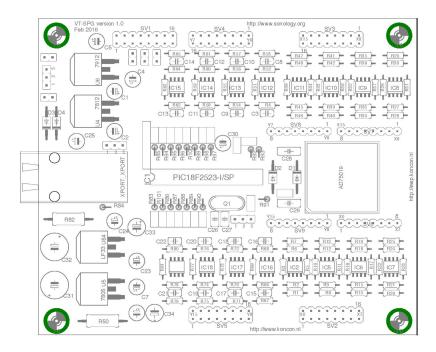

#### 3.7 Printed Circuit Board

To make production of the SPG easier and faster and to offer the students the

possibility to build and construct one, it's a must to design a Printed Circuit Board (pcb). On a pcb all connections are pre-made according to the schematic and the only thing the user has to do is place the components on the right location and solder the pins to the board. The pcb, drawn with EagleCad software, is a straight translation from the circuit-layout. It is a double sided pcb, which means that both bottom and top layer consists of copper connections.

Figure 3.11. SPG printed circuit board.

The left side of figure 3.11 shows the component side, with only the names and the shapes of the components printed on top. The right side of the figure shows both the top (red) and the bottom(blue) copper layers. The big surfaces are ground planes and are used to keep the ground impedance as low as possible (more copper) and it also has environmental reasons - the less copper that is removed, the better.

Figure 3.12. SPG printed circuit boards wired up

# 3.8 The SPG prototypes

To be able to test the hardware design of the SPG and have students practically work with the instrument and share their feedback, I made multiple models to be tested. Since there are multiple standards concerning the connectors in the analogue synthesizer world, the models are provided with different kind of connectors and with different shapes. A

quick reference list of all the models built, can be found in appendix D, page 70.

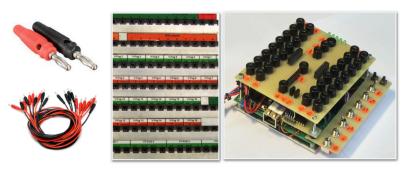

The patch-panel of analogue studio Bea-5 is designed with so called banana connectors. This is a robust connector with only one signal present. The setup of the analogue studio has one collective GND connection for all the modules within the studio. If connections have to be made between these modules, only the signal has to be patched the GND connection is already made. Figure 3.13 on the left shows the banana-connectors and patch-cables and in the middle a small part of the patch-panel from analogue studio Bea-5. On the right side the SPG prototype with female banana connectors, to be interfaced with the patch-panel of Bea-5.

Figure 3.13 Banana connector model

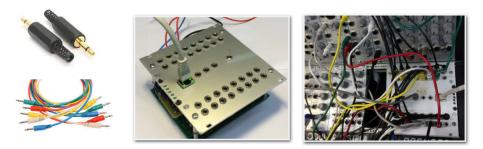

The next implementation of the SPG is the model that communicates with mono minijack connectors. These small connectors are used in a wide variety of modular systems and especially in the Eurorack modular synths, like for example the Doepfer A-100 system. The minijack connectors connect two signals: the GND and the actual signal.

Figure 3.14 On the right, the SPG model with minijack connectors

The model shown in the middle in figure 3.14 is the SPG model that can be build into an Eurorack modular synth. At this point two of these models have been build: one version for the Sonology Doepfer A100 system and one version for Ruben Brovida, who embedded the model into his own modular setup.

The third type of SPG prototype is provided with the 1/4" mono jack. This is a popular connector in the music industry, especially for guitars and keyboards, effects, amplifiers and mixing consoles, see figure 3.15. Due to the size of these connectors, the package of

this model with 35 female 1/4" jack connectors mounted, is somewhat big.

Figure 3.15

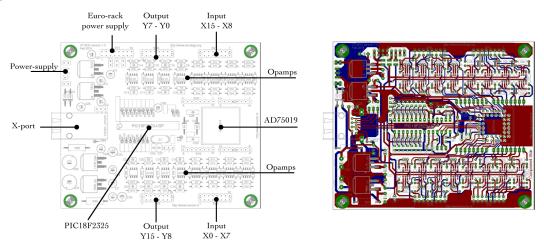

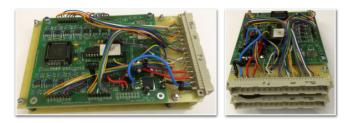

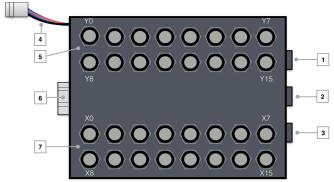

The last practical model of the SPG that is built within the timespan of the research-project, is the version that is implemented into the RC-studio and is constructed on a Eurocard format pcb (printed circuit board). The inputs and outputs, as well as the power-supply, is provided by two 32-pin multi connectors - see figure 3.16.

Figure 3.16. The VC-SPG model for the RC-studio

### 4 Software design

The core of the SPG project is the software and it can be split in two different main applications. The first one is the assembly code that is running inside the microcontroller, processing all the analogue- and digital-signals. This code running inside the Microchip microcontroller is also known as firmware. The second software application is the Max/ Msp-patch running on the host computer, driving and programming the SPG (see figure 4.1).

The Max/Msp patch generates a stream of OSC-messages that drives, programs and controls the SPG. These OSC-messages, explained in chapter 'Communication', page 43, can be generated by any type of software, as long as the format of the OSC-message has the correct syntax. The firmware, however, is the heart of the design and the setup and configuration determine the main physical properties of the SPG. Choices made within the firmware have time-related consequences and thus, have a big influence on the musical behavior of the SPG.

Figure 4.1 Max/Msp patch and Assembly determine the properties of the SPG

#### 4.1 Assembly- firmware

It is inevitable to explain something about the programming language Assembly. The firmware written for the SPG consists of around 3000 lines of code - a huge part of the projects' development time and important parts of the properties of the SPG are determined by this firmware and its configuration. It would be beyond the scope of this thesis to cover the complete architecture of microcontroller and the Assembly language in total, but a glimpse at the technology used is essential for this research project to give a better insight and understanding.

Assembly is a low level computer programming language that is specified for certain types of controllers. An Assembly program written for one specific device or brand, cannot easily be re-programmed into another device due to the architecture differences between the devices. Also the code and the structure of the program very much depends on the architecture of the controller.

The PIC18F2523 microcontroller, an 'enhanced flash microcontroller with 12 bit A/D nano watt technology' (Microchip user-manual), is an 8-bit RISC-controller with powerful features. This microcontroller is, in fact, a small computer complete with inputs,

outputs and power connections. Instead of the normal mouse and monitor, a microcontroller has physical pins with voltages between 0 and 5V acting as inputs and outputs. In visual aspect it does not look like a computer at all. It is a chip, an Integrated Circuit or abbreviated as IC. It has program memory, data memory, multiple timers and counters, communication ports and special function registers.

Writing firmware for this controller means writing the program code on bit-level, the lowest programming level. This actually means the programmer (that would be me) has to literally think in 'bits' and 'bytes', thinking in time slices of 20 nanoseconds or having to realize that over 5 million steps of code will be executed in 1 second.

Another subject that has to be indicated, is the importance of the registers inside the microcontroller. The special function registers (SFR) within the microcontroller, contain data or information, which determines the way the microcontroller operates in realtime. At startup or initialization, all registers are filled with data (8-bit or 16-bit words). Therefore registers can be compared with switches that have to be set or cleared to create a certain configuration. The main and most important register in the controller itself is the working register called Wreg. All commands, operations and actions will be processed through this register Wreg. Moving numbers from one place to another, adding numbers, shifting numbers, comparing variables, (almost) nothing can be accomplished without Wreg.

Another important register is the status-register. In this status-register the actual 'state' of the controller can be checked after an operation or arithmetic action. For instance if two numbers are added and the outcome is a number larger than 255 (8-bit number maximum), the corresponding carry-bit within the status-register will be set and can then be checked by the next instruction.

To give a rough overview, the Assembly language instructions can be divided into four big basic categories: byte-oriented operations, bit-oriented operations, literal operations, and control operations. Every operation or instruction consists of three operands. Some instruction examples of the 4 different categories:

Examples of byte oriented operations / instructions:

andwf porta [AND the content of the Wreg with register porta]

incf counter [increment variable counter with 1]

Examples of bit oriented operations:

**bcf** porta, 1 [bit clear f // clear bit 1 of register porta]

btfss porta, 3 [bit test f and skip if set // test bit 3 of porta and skip the next

instruction if this bit is set]

Examples of <u>literal oriented operations</u> / instructions:

movlw 0x00 [move literal into Wreg // move hex number 0x00 into Wreg]

**xorlw** 0x2A [Xor literal with Wreg // Exclusive OR content of Wreg with 0x02A]

Examples of control instructions:

call wait [call subroutine wait]

goto write [goto subroutine write]

With regards to the design of the SPG, many reasons can be given for using Assembly and a fast microcontroller. First of all, my familiarity is based on the usage of the Microchip controller series, given the fact that I have designed extensively with this technology. I'm experienced with the design of electronics in combination with the microcontrollers running Assembly. This experience gives me the possibility to make a better design in the time window available for this research - I do not have to learn a complete new language.

The second reason, and the most important one, is that being able to program Assembly is a very powerful way to maintain control over 'time' during operation. This means the time elapsed in an Assembly program can easily be managed and calculated. Every instruction only takes one or two instruction cycles (clock cycles), from which the timelength is known. Creating some loops or equivalent actions can always be brought back to the actual real time elapsed within that loop.

Higher level programming languages like C++, Java, Pascal or Arduino's 'processing' need to be compiled with external compilers, bringing the program back (down) to machine language. This translation of the written program with the aid of a third party compiler is a conversion or translation in which this exact level of time control is lost. Depending on the quality or brand of the compiler used, the actual generated machine code can differ and so will the elapsed time of different loops and routines. When depending on fast time-critical communication, it is important and absolutely necessary to keep control over 'time' in the written code. This control can be obtained when programming in Assembly.

The best way to explain the way Assembly works is by using an example. In the next paragraph follows more detailed information about how the switching array can be filled with a new preset and activated - the core activity of the SPG.

#### 4.2 Data transfer from microcontroller to matrix

The core assembly process in this project is to drive the Analog Devices AD75019 switching array chip. This  $16 \times 16$  matrix chip is capable of switching 256 switches simultaneously. Changing the status of these switches takes time. It takes the controller 568 µsec (=  $568 \times 10^{-6}$  seconds) to write 256 bits from the controller output into the

switching array. In other words, within 1 second, this switching array can jump 1700 times between different presets (1.7kHz).

Another important process in the setup is reading the incoming opensoundcontrol (OSC) information from the computer connected to the controller. Through external software (for example Max/Msp or Super Collider), the controller can receive up to 32 presets, to be stored into the local memory and later to be sent to the switching array when the sequencing-mode is active. Or the received OSC-message contains a new patch that will be activated immediately after it has been received.

How can an eight bit controller like the 18F2523 drive the AD75019 and simultaneously read incoming data from the web server or computer? Throughout this research project it has become more clear that speed and timing matter. The speed of switching between presets is an important variable when the SPG is used as a generator. In this chapter the importance of this speed issue will be highlighted by describing the complete process of transferring data between the controller and the switching array. This is the most essential process of the whole generator.

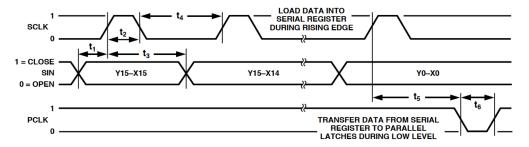

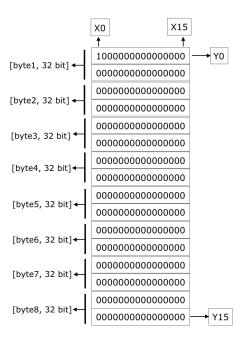

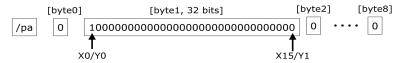

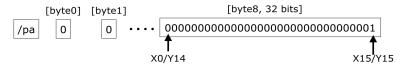

Before the time related process can be explained, it is important to know how the controller is communicating with a peripheral. Take a look at the timing diagram below, figure 4.2. Peripherals like the AD75019 switching array do have 3 data communication lines: data input, a clock input or shift clock (Sclk) and a storage clock (Pclk). To write a full preset from the controller to the switching array, 256 bits have to be transferred one by one with the aid of these 3 lines only. See also chapter 6 'SPG communication' for the exact syntax of the data.

Every bit represents one switch within the array (1=open and 0=closed). The first bit that will be 'clocked' into the array is in fact the last bit of the matrix: (x15,y15). After 256 clocks or positive edges, the first bit (x0,y0) is set into place. If all bits are in place or 'clocked-in' the storage-clock signal will change value. This will result into an activation of the preset itself and all switches change to their new position simultaneously.

Figure 4.2. Timing diagram of communication (SPI, Serial Peripheral Interface)

The clock-signal, SCLK, is generated by port RC1 of the controller and switches between 0V and 5V at a very high speed. Within the Assembly code port RC1 is set and

reset sequentially, to generate a clock-pulse. On a rising edge, the value of the data input SIN will be 'clocked in'. The clock, the data and the storage clock are generated by the assembly program, running within the controller. Port RC0 is the data output from the controller, connected to the SIN (data input) of the array. Port RC2 is the PCLK - the most important signal. When the PCLK is set low, the whole preset is activated.

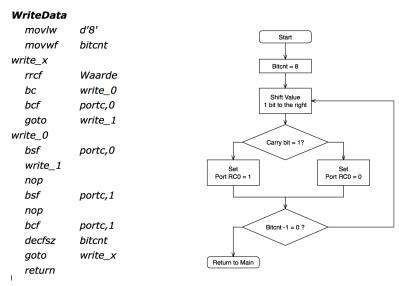

It is now easier to look at the corresponding Assembly code that realizes this communication. The name of the routine in the example below is called 'WriteData'. Within the main program of the generator, this part of the code is named a sub-routine. This sub-routine is 'called' from within the main routine with the value to be sent to the switching array stored in the variable 'Waarde'. So, if a valid value has to be written to the AD75019, this routine 'WriteData' is executed. The routine only writes 8 bits in a row, hence the value 8 at the beginning of the code. For writing one complete preset from the processor to the AD75019 switching array, this particular piece of code will be called 32 times (8x32=256). The flowchart on the right shows the sub-routine in graphical format.

Figure 4.3. Flowchart with the corresponding Assembly code.

During the first two instructions the counter is set to the value of eight - only 8-bits will be transferred in this routine. First loading the Wreg with the decimal value 8 ( = movlw d'8' // move literal into Wreg) and then moving the value of the Wreg to the variable 'bitcnt' ( = movwf bitcnt // move content Wreg to bitcnt).

To be able to determine the value of a particular bit, it is best to just rotate (or shift) the value 1 bit to the right (rrcf waarde // rotate right through carry f) through the carry. If the result of this action sets the status registers carry bit, the data port RC0 can be set to one (= bsf port,0 // bit set f). If the carry bit is cleared, port RC0 will be set to zero (= bcf portc,0 // bit clear f). If the data pin, or port RC0 has its right value, the Sclk pin (port RC1) will be set high and low, thus creating a rising edge. To make this clock pulse longer in time, due to minimum values, a nop instruction is placed in between (nop = no

operation).

The last decision in this sub-routine is to check if all 8-bits have been dealt with. Decrement the counter value with one (bitcnt-1) and check if the resulting value is zero. As stated before in this chapter, the time that is needed for writing the whole preset from the controller to the switching array, can now be determined accurately by calculating exactly how many instructions it takes. In practice, a good quality oscilloscope can also provide precise information about the length of the whole process - receiving the OSC-message from the computer, storing it and sending it to the switching-array.

The last signal that has to be generated in order to really activate the 256 bits, is the Pclk (see figure 4.3). In the design of the SPG this Pclk signal is connected with port RC2 of the microcontroller (figure 4.3). After writing 256 bits, port RC2, which is normally high, has to be cleared and set in sequence to provide the AD75019 with a falling edge. If the falling edge is detected, the preset with all of its 256 bits is activated and the SPG switches. Within the design of the SPG, this negative pulse on RC2 is actually one of the most important timing related pulses. Within the Assembly code this routine is called 'metro'.

## 4.3 The SPG main-routine

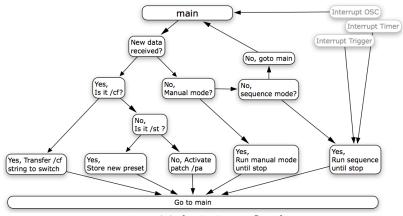

The heart of the assembly code of the SPG is the main-routine. This routine is actually a loop containing jumps and calls to different sub-routines, continuously checking if something internal or external has changed. It is a continuous process and will only stop if the power is switched off. Also notice that the main program-loop consists of checking exclusively the state of 'bits', resulting in questions that only can be answered with Yes or No.

Consult the flowchart in figure 4.4. Starting from the top, the first process to be checked is if new valid OSC-information is available. If the answer is no, the next status to be checked is the manual mode. Is the manual-mode switch active? If this is not the case, the last status to be checked is the sequence mode and if that question is also answered with No, the whole loop starts all over again.

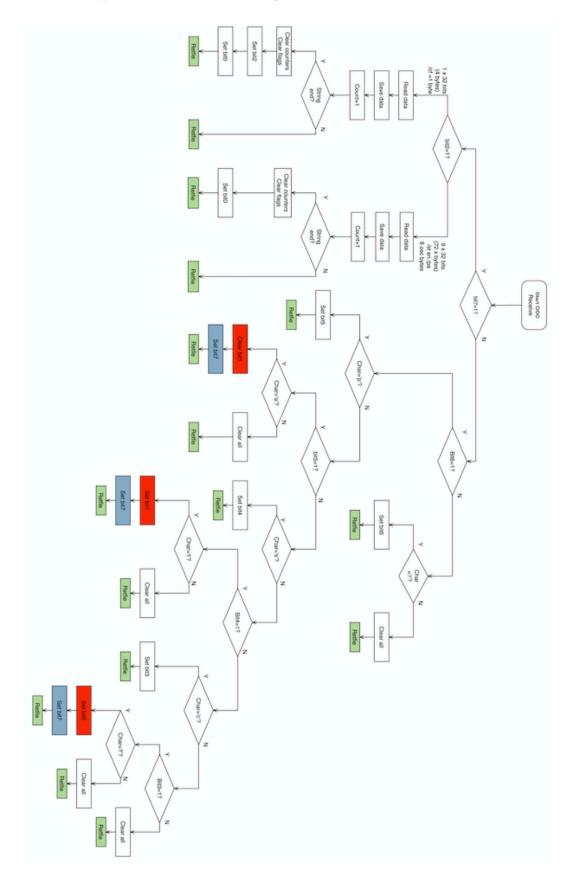

Figure 4.4 The SPG main-flowchart.

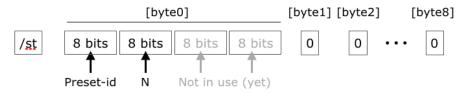

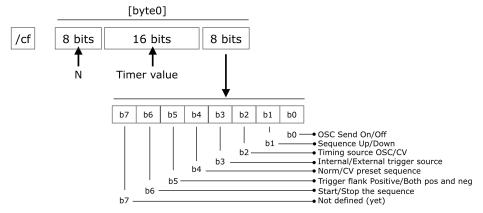

If new data is available (new data received = yes), there are 3 different OSC-address type tags to be checked. If it is a /cf message (configuration), then the status of the SPG has to change - it has to for example start with sequencing or store new values for timing. Should it pertain to a /st (store) message, the received patch has to be stored in the right memory location. Lastly, if the block in the middle is dealing with a /pa message, this patch has to immediately be made active.

The 3 light-gray circles on the top/right are an indication of the interrupt processes that can occur. These interrupts are triggered by external processes (trigger pulses) or internal processes (timer counters).

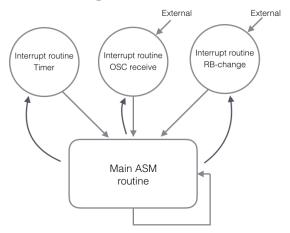

#### 4.4 External and internal interrupts

An important advantage of the microcontroller is the use of interrupts. Like in normal life, every process can be interrupted. The question is how to handle this situation and which next process will follow up this interrupt. Can you proceed with the same subject, when somebody just interrupted your 'actual action' or do you ignore the interrupt? The trick is to store the 'actual action' just before you react on the interrupt and deal with it. All these actions in a sequence within Assembly are called an 'interrupt handling routine'.

The microcontroller has many different kinds of interrupts. There are internal- and external-interrupts, high-priority and low-priority interrupts and all of them have to be configured during initialization.

The design of the SPG uses a few important interrupts, which will be explained in this paragraph. The functionality of the SPG is based upon 3 different kinds of interrupts and they all have a high priority - they have to be taken care of right away. These interrupts do really 'interrupt' the main program loop. Figure 4.5 shows the block diagram of the main routine in combination with the interrupts.

Figure 4.5 Main routine with 3 types of interrupt.

The first interrupt is the reception of new OSC-messages. When new data arrives, it has to be processed right away. The second one is the internal timer interrupt. After a certain amount of time, mainly used during sequencing, the timer sets an interrupt, stating the adjusted time has passed. The third interrupt is the so called 'interrupt on change'. If a signal connected to a particular pin changes value from low to high (0V-5V), or high to low (5V-0V), it will generate an interrupt. This 'interrupt on change' is an ideal way to time-sync the SPG with external processes.

### 4.4.1 Receive OSC-message interrupt

This interrupt occurs when a new OSC-message is received and it activates the EUSART<sup>11</sup> RCIF flag. This flag, or bit, is set high when new valid data is received and is waiting to be processed. The processing of the received data is done within the interrupt

routine, after the values from the main routine are being put to stack.

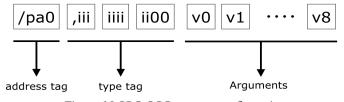

As you probably know, an OSC-message is build up by three different tags, starting with the address tag, the first thing that has to be checked within the routine is the address tag. Is it the right value and is the data intended for the SPG? The values intended for the SPG are: /pa, /st and /cf (see chapter OSC-communication) and all three call for different actions within the SPG (activate patch, store patch, control SPG). As a result not only the address-tag has to be checked, but also the linked process has to be determined. The flowchart or graphical representation of the whole (complex) interrupt routine can be found in appendix E.

The OSC-message 'receive interrupt-routine' will handle the interrupt and sets the corresponding bits for the main routine to work with. If a /pa OSC-message has been received, the main routine should activate the corresponding patch right away. If the /st OSC-message is received it should store the preset at the right memory location and if the OSC-message has a /cf address tag, the SPG will change its present state.

#### 4.4.2 Timer interrupt

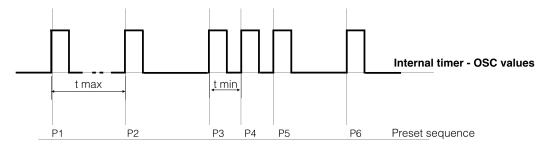

When the SPG is sequencing it makes use of the internal timer (timer0). A timer is a 16-bit register that counts every program step within the code. It actually increases its value with 'one' on every instruction (cycle). When the /cf OSC-message contains a 16-bit timer value that is the source of the sequence speed, this number will be compared with the value of the internal timer. When both are equal an interrupt will occur and the SPG will step to the next preset stored in its memory.

Hence sequencing with the SPG is done in sync with its internal timer and this results in a very stable and precise timing, which for musical applications, is critical.

Also in the CV-speed mode, when the SPG is reading an external voltage to be converted into a sequence speed, the internal timer is used. First an analogue to digital conversion (ADC) is carried out and the result, a 12-bit number, is the basis for the timer to generate time based interrupts. The specific code for the interrupts can be found in appendix F.

#### 4.4.3 Signal on change interrupt

PortB of the microcontroller has some great features and one of these features is the 'interrupt on change'. When one pin of portB changes its value from 0V to 5V or from 5V to 0V, an interrupt is generated. These pins are connected to the external trigger input of the SPG. When the external trigger signal changes value, the SPG will activate a new

preset and write this to the audio matrix.

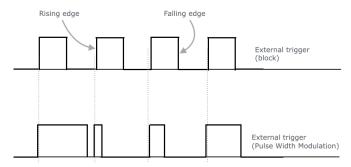

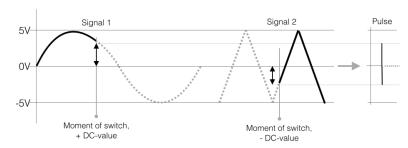

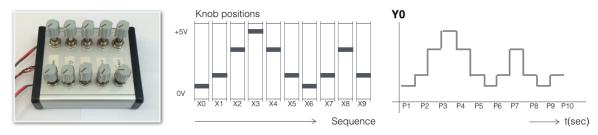

Take a look at figure 4.6. Since there are two different 'signal on change' interrupts, one for the rising edge and one for the falling edge it is possible to have the SPG step to the next preset on both edges, introducing modulation within the sequence when a pulse width modulation signal is connected. The preset will be activated in different time lengths.

Figure 4.6. Example of positive- and negative edges with block and PWM.

### 4.5 Sequence routine

The second important routine defining the functionality of the SPG, is the sequence routine that steps through the local stored presets and is constantly checking the status of the received OSC-message (/cf string). The SPG can sequence based upon the internal timer, an external control-voltage and the external trigger signal. If the external trigger is active, which is checked within the initialization of the routine, it can switch on both edges or only on the rising edge(see page 38). The whole sequence flowchart is shown in figure 4.7. The upper part is the initialization of the sequence routine and the lower part is the actual sequence part.

Figure 4.7. The sequence flow chart (version asm90)

As described in the chapter 'SPG Features' (page 35) the SPG can sequence up or down through the local stored presets or the order of the sequence can be determined by an external control voltage (cv-preset-id). If the order of the sequence is determined by the external control voltage, there is no timing involved. If the control-voltage changes its value, the preset linked to this value will be activated immediately.

The SPG design contains three sources that determine the timing or speed of the sequence: the received 16-bit OSC-number as part of the /cf OSC-message, the external control-voltage and the external trigger pulse. The number received by the /cf OSC-message is transferred directly to the onboard timer of the processor and activated. If the control-voltage to speed option is active, the AD-convertor measures the value of the voltage and the resulting 12-bit number is transferred to the same onboard timer. The external trigger does not work in combination with the onboard timer. The value change of the trigger pulse, generates an 'interrupt on change' and this controls the speed of the sequence.

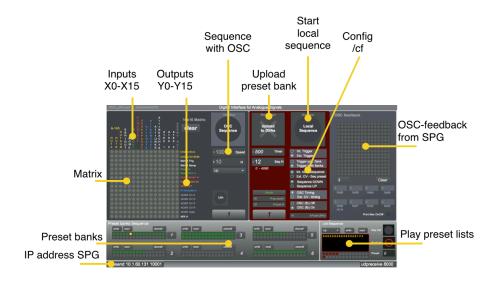

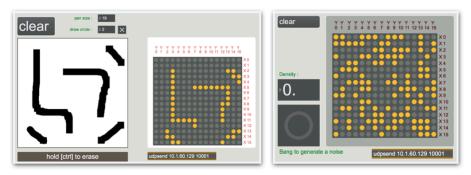

# 4.6 Max/Msp Patch

To control the full functionality of the SPG, I created a software patch with Max/Msp,

that enables the user to fully control the SPG and generate presets in many different ways. It hosts the functionality to store many presets in special preset-banks and generate random series, or play complete pre-defined lists of presets. As will be stated in the chapter 5 'Features' (page 37), driving the SPG directly from the Max/Msp patch is very well possible, but it has its time or speed limits, which can reveal unstable behavior, especially at high frequencies. This is the reason why presets made within the Max/Msp patch can be uploaded to local memory of the SPG, so no new data has to be sent back and forth every time a preset changes; it saves time.

The red part within the layout of the Max/Msp patch is related to the uploading of presets to local memory and it shows the controls to set the SPG in the preferred configuration (figure 4.8).

Figure 4.8 The Max/Msp patch, linked to asm version 85.

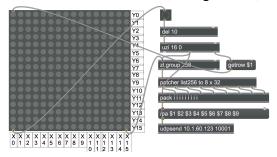

The configuration-bits, a part of the /cf OSC-message (see page 47) are the switches to set- or reset functions like external- or internal trigger and it enables the selection of different control voltages. On the left side of the layout the actual matrix is located with its inputs on top and the outputs on the right.

Below the actual matrix, presets can be stored in preset-banks. In this patch setup 6 preset-banks are created with each 32 presets. If a certain preset-bank is selected, indicated by the big number in the middle, it is this bank which serves as the source of the sequence. The order of the sequence is limited to up, down or pendulum and there is also an option to have the sequence-order determined by a list.

On the right from the matrix, the control to start/stop the OSC-sequence and change speed and preset-order.

On the right side of the layout another matrix is located. This matrix shows the received

OSC-messages from the SPG itself and provides the user with accurate feedback. The number-boxes underneath the feedback matrix show the content of the actual registers within the microcontroller. During the design and test-phase it's very practical to have this information available, but for the future user it is optional to use. A more detailed description on the Max/Msp patch can be found in Appendix G.

The presets are stored in the designated preset banks. In the right corner of the patch, the numbers can be edited to generate a list of preset-sequences. The core of the Max/Msp patch is based on the standard matrix-control object. This object generates row- and column data with the corresponding value of the cell. If a cell is selected, the output generates [column-number], [row-number], [0 if off and 1 if on]. This series of three numbers is converted into the right OSC-message pointing at the right cell within the 16x16 matrix.

To convert the standard matrix-control output to the right OSC-format, some complex steps have to be taken to achieve this conversion (see figure 4.9).

figure 4.9 Max/Msp standard matrix object with conversion.

#### **5 VC-SPG Features**

The main basic structure of the VC-SPG is described in chapter 2 and the more technical considerations are described in the chapters 3 and 4. In this section the focus will be on the features of the SPG. How does the sequence through presets actually work and what are the specifications of the external control signals? What about the sound quality of the SPG and are clicks audible when all 256 switches change position simultaneously?

### 5.1 Initial startup

Initially the SPG should be connected to the computer with a standard network-cable and it has to be connected to the power (-12V, +12V, +5V and GND). The Max/Msp patch that drives the VC-SPG generates the 3 main OSC-messages to drive and upload presets. Due to the large number of matrix options it's a good habit to keep a concise and clear labelling approach.

If all connections are made, the patching can start. Clicking on the crossing in the matrix-object will change the colour from gray to yellow, indicating the connection is now active. By selecting multiple cross-points and thus making multiple connections between inputs and outputs of different modules, sounds can be generated. If the preset, or patch sounds like it needs to be stored, the standard preset object located in the left down-corner of the Max/Msp patch can be used. A preset can be stored by Shift-Clicking a location. The small 'dot' will change colour from gray to green, indicating the preset is stored (see page 32).

#### 5.2 Audio in's and out's

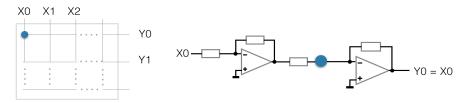

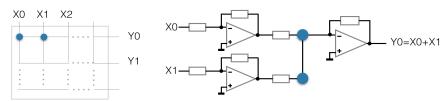

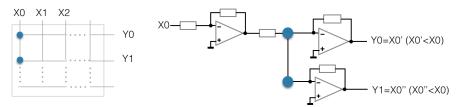

One of the main features of the interface is the input-adding function, which is an important part of the design. By selecting multiple inputs of the matrix to be routed to the same output, the real sum, or mix, of the signal will be available at the output. The summation of the signals is obtained with the use of Opamps<sup>12</sup> configured in a double inverting-amplifier setup. On the left side of figure 5.1 the input X0 is selected to be routed to output Y0 (the blue dot). Because both input and output of the matrix are buffered with an opamp circuit configured to be an inverting amplifier, connecting them together with the matrix will create a series connection of two independent inverting-amplifiers. A twice inverted signal equals a not inverted signal. The output result would be: -Y0 = -X0, or Y0=X0

Figure 5.1. Opamp configuration with X0 routed to Y0 (blue dot).

Figure 5.2. Opamp configuration with X0 and X1 routed to Y0( Y0=X1+X2).